# Lecture Notes in Computer Science

4745

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

*University of Dortmund, Germany*

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

# SDL 2007: Design for Dependable Systems

13th International SDL Forum Paris, France, September 18-21, 2007 Proceedings

#### Volume Editors

Emmanuel Gaudin PragmaDev SARL 18, rue des Tournelles, 75004 Paris, France E-mail: emmanuel.gaudin@pragmadev.com

Elie Najm ENST Département Informatique et Réseaux

46, rue Barrault, 75634 Paris Cedex 13, France

E-mail: Elie.Najm@ENST.fr

Rick Reed

Telecommunications Software Engineering Limited The Laurels, Victoria Road, Windermere, Cumbria LA23 2DL, United Kingdom E-mail: rickreed@tseng.co.uk

Library of Congress Control Number: 2007934912

CR Subject Classification (1998): C.2, D.2, D.3, F.3, C.3, H.4

LNCS Sublibrary: SL 5 – Computer Communication Networks and Telecommunications

ISSN 0302-9743

ISBN-10 3-540-74983-7 Springer Berlin Heidelberg New York ISBN-13 978-3-540-74983-7 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12161393 06/3180 5 4 3 2 1 0

## **Preface**

This volume contains the papers presented at the  $13^{th}$  SDL Forum, Paris, France entitled "Design for Dependable Systems" and reflects the intent to have a balance between experience reports and research papers related to System Design Languages.

The language that was at the heart of the first few SDL Forums was the ITU-T Specification and Description Language defined in Z.100, and the application domain was almost entirely fixed-line telephone communication. Mobile telephony was for the super-rich and electronics in cars was just for radios.

Ever since its inception, 30 years ago, the Z.100 language has been used for model-driven development in the telecommunication industry. Nowadays, model-driven engineering is a must for all industries and has been generalized by OMG to all application domains as covered by a paper on an automotive case study in this volume. What has been happening over the past few years is that the infrastructure has been put in place providing good support for the model-driven paradigm, so that the economic benefit of the approach makes it more of a necessity than a choice for designing dependable systems. The experience report from Motorola in this volume underlines this trend.

Although the SDL Forum Society that organizes these SDL Forums has it roots in telecommunications, the System Design Languages needed for modeling in that industry are applied in other real-time engineering domains such as aerospace, the ubiquitous Bluetooth devices, and railways. For the last few years all modeling languages and technologies have had a tendency to converge towards UML, and since UML 2.0 and its profile definition capability came out, there is now an amazing number of diverging profile proposals based on older technologies. This was reflected in the conference programme with tutorials on SysML, SDL-RT, MARTE, and Z.109 covering different aspects of system modeling. An example in this volume is the paper that utilizes the UML 2.0 Testing Profile.

This latter paper is one of a number that shows the continuing interest and developments in the ITU-T Testing and Test Control Notation (TTCN). Although much of the evolution of TTCN has been through the work of ETSI, it is still largely seen as an ITU-T standard. In some ways this makes sense as ITU-T re-publishes the ETSI revisions of TTCN as a truly international standard (Z.140 series). TTCN is widely used with the ITU-T Message Sequence Chart (Z.120) and Specification and Description Language (Z.100 series). These are also used with another ITU-T product, Abstract Syntax Notation One (X.680 series), which is used to define protocol data units with their associated encoding rules (X.690 series). However, these languages are not thought to be adequate to capture requirements. A new language for User Requirements Notation (Z.150 series) is in progress, which includes Use Case Maps — covered by another paper in this volume.

So with all these ITU-T languages for system design, what is the role of UML?

UML is seen, as its name implies, as a unifying concept between languages. Because UML leaves a number a semantic issues open and even states frequently that there is no specific notation for a particular concept, it is in reality largely a framework that has to be populated with specific semantics and notations before it can be used to completely develop products. One route is to choose a particular UML tool, whose implementation (such as writing actions in C or Java) will have fixed certain issues, but at the cost of potentially being locked into that tool. Another route is to provide UML profiles for existing languages, thus not only binding UML to the semantics and notation of the language, but also providing some glue between different notations. It is the latter route that the ITU-T is taking (albeit rather slowly), with Z.109 being approved in 2007 as the UML profile for Z.100. Other profiles are in the ITU-T work plan for X.680, Z.120, Z.140 and Z.150. A related path is presented in the first paper in the volume, providing a meta-model for (a subset of) Z.100.

UML also has another role. If you ask someone who claims to be using UML which diagrams they use, often the reply will be that they mainly use Class Diagrams and Object Diagrams. The other 11 types of UML diagrams are used less frequently and some quite rarely (if at all). This is partly because the Class Diagrams and Object Diagrams meet a need that is not well met by other notations. Even the ITU-T in its 1996 Z.100 SDL+ methodology supplement suggested using diagrams in the Object-Modeling Technique notation (a forerunner of UML subsumed into UML in the unifying process). This is why it is natural to use these diagrams with the ITU-T languages: UML is frequently used for class and object modeling with Z.100 and other state machine languages in this volume and elsewhere. UML therefore not only provides the glue, but itself provides an important member of a set of System Design Languages.

Although the original Z.100 of 30 years ago was a paper and pencil language, none of this engineering today would be practical without computer-based tools because the systems in question are much more complex. This is evident from most of papers. As well as tools to directly support System Design Languages, included in this volume are papers on a real-time operating system and the use of probability modeling to analyze realistic-size networks without encountering state space explosion. At first glance, it may seem that these papers are not relevant, but you will probably change your mind when you read the papers, as a key issue in both cases is performance. There are many factors involved in the design for dependable real-time systems, so it is hard to predict what might be relevant for a future SDL Forum.

#### Thanks

A volume such as this could not, of course, exist without the contributions of the authors, who are thanked for their work.

The Programme Committee were also the reviewers of the papers, and are thanked for their work selecting the papers and the programme.

Irfan Hamid of ENST is thanked for his editorial assistance in preparing this volume.

The organization was greatly assisted by the various sponsors that provided valuable support. SDL 2007 was sponsored by:

- Centre National de la Recherche Scientifique

- Cinderella

- France Telecom

- PragmaDev

- Télécom Paris École Nationale Supérieure des Télécommunications (ENST)

- Telelogic

July 2007

Emmanuel Gaudin Elie Najm Rick Reed

# Organization

Each SDL Forum is organized by the SDL Forum Society with the help of local organizers. The Organizing Committee consists of the Board of the SDL Forum Society plus the local organizers and others as needed depending on the actual event. For SDL 2007 the local organizers from PragmaDev and ENST need to be thanked for their effort to ensure that everything was in place for the presentation of the papers in this volume.

## Organizing Committee

Chairman, SDL Forum Society Rick Reed (TSE Ltd.)

Treasurer, SDL Forum Society Martin von Löwis (Hasso-Plattner-Institut) Secretary, SDL Forum Society Andreas Prinz (Agder University College)

Conference Chair Emmanuel Gaudin (PragmaDev)

Programme Committee Chair Elie Najm (ENST)

## Programme Committee

Daniel Amyot (Université d'Ottawa, Canada)

Reibert Arbring (Ericsson, Sweden)

Rolv Bræk (NTNU, Norway)

Eric Brunel (PragmaDev, France)

Pierre Combes (France Telecom, France)

Philippe Desfray (Objecteering Software, France)

Laurent Doldi (Isoscope, France)

Anders Ek (Telelogic, Sweden)

Jaqueline Floch (SINTEF, Norway)

Birgit Geppert (Avaya Labs Research, USA)

Reinhard Gotzhein (Universität Kaiserslautern, Germany)

Jens Grabowski (University of Göttingen, Germany)

Susanne Graf (Verimag, France)

Peter Graubmann (Siemens, Germany)

Loïc Hélouët (INRIA Rennes, France)

Paul Herber (Sandrila, UK)

Dieter Hogrefe (ETSI - MTS, Germany)

Eckhardt Holz (University of Potsdam, Germany)

Ferhat Khendek (Concordia University, Canada)

Tae-Hyong, Kim, KIT, Korea)

Shashi Kumar (Jönköping University, Sweden)

Philippe Leblanc (Telelogic, France)

#### X Organization

Vesa Luukkala (Nokia, Finland)

Anna Medve (University of Pannonia, Hungary)

Pedro Merino Gómez (University of Malaga, Spain)

François Michaillat (Alcatel, France)

Birger Møller-Pedersen (University of Oslo, Norway)

Elie Najm (ENST Paris, France)

Patrik Nandorf (Ericsson, Sweden)

Ian Oliver (Nokia, Finland)

Anders Olsen (Cinderella, Denmark)

Benoit Parreaux (France Telecom, France)

Javier Poncela González (University of Malaga, Spain)

Andreas Prinz (Agder University College, Norway)

Rick Reed (TSE, UK)

Manuel Rodríguez Cayetano (University of Valladolid, Spain)

Eldor Rødseth (SystemSoft, Norway)

Alain Rossignol (Astrium, France)

Richard Sanders (SINTEF, Norway)

Amardeo Sarma (NEC, Germany)

Ina Schieferdecker (Fraunhofer FOKUS, Germany)

Bran Selic (IBM Rational, Canada)

Edel Sherratt (University of Wales Aberystwyth, UK)

Martin von Löwis (Hasso-Plattner-Institut Potsdam, Germany)

Thomas Weigert (Motorola, USA)

## SDL Forum Society

The SDL Forum Society is a not-for-profit organization that in addition to running the SDL Forum:

- Runs the SAM (System Analysis and Modeling) workshop every 2 years between SDL Forum years.

- Is a body recognized by ITU-T as co-developing the Z.100 to Z.109 and Z.120 to Z.129 and other language standards;

- Promotes the ITU-T System Design Languages.

For more information on the SDL Forum Society, see www.sdl-forum.org.

# Table of Contents

| Model Driven Engineering                                                      |     |

|-------------------------------------------------------------------------------|-----|

| A Model-Based Standard for SDL                                                | 1   |

| Model Driven Development and Code Generation: An Automotive Case Study        | 19  |

| Experiences in Deploying Model-Driven Engineering                             | 35  |

| Testing                                                                       |     |

| TTCN-3 Quality Engineering: Using Learning Techniques to Evaluate Metric Sets | 54  |

| Using TTCN for Radio Conformance Test Systems                                 | 69  |

| Testing UML2.0 Models Using TTCN-3 and the UML2.0 Testing Profile             | 86  |

| Language Extensions                                                           |     |

| Specifying Input Port Bounds in SDL                                           | 101 |

| Translatable Finite State Time Machine                                        | 117 |

| Enhanced Use Case Map Traversal Semantics                                     | 133 |

# Implementation

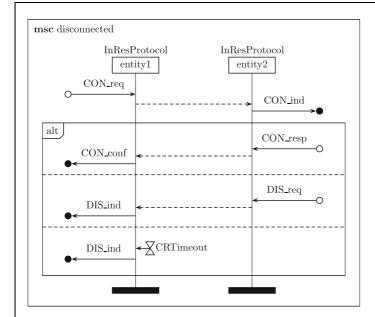

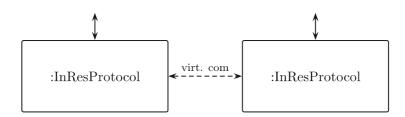

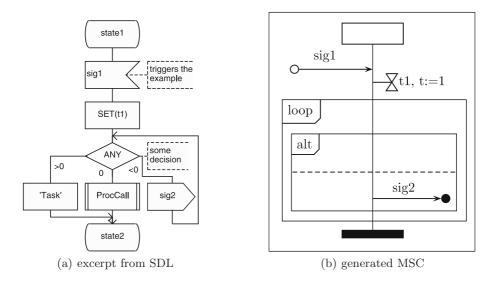

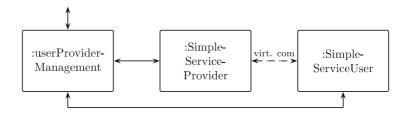

| Automated Generation of Micro Protocol Descriptions from SDL  Design Specifications                                      | 150 |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| Synthesizing Components with Sessions from Collaboration-Oriented Service Specifications                                 | 166 |

| Experiences in Using the SOMT Method to Support the Design and Implementation of a Network Simulator                     | 186 |

| Modeling Experience and Extensions                                                                                       |     |

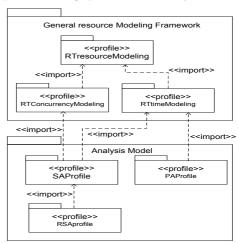

| Consistency of UML/SPT Models                                                                                            | 203 |

| Formal Verification of Use Case Maps with Real Time Extensions Jameleddine Hassine, Juergen Rilling, and Rachida Dssouli | 225 |

| Using Probabilist Models for Studying Realistic Systems: A Case Study of Pastry                                          | 242 |

| OpenComRTOS: An Ultra-Small Network Centric Embedded RTOS Designed Using Formal Modeling                                 | 258 |

| SDL Design and Performance Evaluation of a Mobility Management Technique for 3GPP LTE Systems                            | 272 |

| Author Index                                                                                                             | 289 |

## A Model-Based Standard for SDL

Andreas Prinz<sup>1</sup>, Markus Scheidgen<sup>2</sup>, and Merete S. Tveit<sup>1</sup>

<sup>1</sup> Faculty of Engineering, Agder University College Grooseveien 36, N-4876 Grimstad, Norway {andreas.prinz,merete.s.tveit}@hia.no

<sup>2</sup> Department of Computer Science, Humboldt Universität zu Berlin Unter den Linden 6, 10099 Berlin, Germany scheidge@informatik.hu-berlin.de

**Abstract.** Language descriptions have much information captured in plain (English) text, and even the formalised parts are often informally connected with the overall language definition. These imprecise descriptions are hardly usable to automatically generate language tool environments out of the language standard. SDL has already managed to define syntax and semantics in a quite formal way. Currently, this formality is connected by using different types of grammars. Meta-models, however, have proven to be a good way of expressing complex facts and relations. Moreover, there are tools and technologies available realising all language aspects based on completely formal and still easily understandable meta-model-based descriptions. This paper is about an experiment of combining all these existing techniques to create a definition of (a subset of) SDL. This allows to have immediate tool support for the language. This experiment includes the language aspects concrete syntax representation, static semantic constraints, and language behaviour. It turns out that this is almost possible.

#### 1 Introduction

Model Driven Development (MDD) uses models to describe systems on a higher level of abstraction. This abstraction, i.e. hiding of much detail, is possible because models are instances of more and more complex modelling languages, which provide more and more specific concepts. Therefore, there is a need for more complex and (domain) specific modelling languages. Furthermore languages in an MDD environment are only meaningful if they come with a comprehensive tool environment. So there are two challenges: creating a human readable language standard and providing tool support for the language.

It is obvious that it is necessary to have a description of the language first. We will call such a description a meta-model. Today, there are several language description techniques and meta-tools that allow to describe and realise single language aspects like concrete syntax, static semantic analysis, model execution, or code generation. Tooling can be achieved by manually building language tools or by creating modelling tools automatically from the language description. In the latter case, the language description has to be completely formal.

The contribution of this paper is a combination of existing and new techniques forming one cohesive language description with the possibility to create a complete tool environment from it. We start with a representative sub-set of SDL (this sub-set provides all features necessary for the well-known camera example), and create meta-model-based descriptions that can function as a human-readable standard and an SDL tool environment including textual and graphical editors, static semantic checker, and model simulator.

The current SDL standard [8] with its formal semantics specification [7] already showed that most language aspects can be described formally without ambiguities. In [3], Prinz et. al. showed that even aspects that are usually described informally, like language behaviour, can be described formally allowing tools to be created from such formal descriptions in an at least semi-automated way. In [4] we discussed the possibility to use meta-modelling as the basis for integrating different languages and tools with each other. We already successfully evaluated the possibilities for automated tool support based on meta-models in the context of domain specific languages in [10,14].

In this paper we explain how different meta-modelling techniques work together. We focus on the two main purposes given above: how to present the language description in a user-friendly way and how to use the description for generating tools. Although in an ideal world, these two purposes would coincide, we could not achieve a complete match in this experiment.

The paper is structured as follows. In Sect. 2 we will introduce the different language aspects that we used in this experiment together with their relation to each other. The subsequent sections will present the approaches and technologies that we used to describe the different aspects one by one, namely structure (Sect. 3), constraints (Sect. 4), representation (Sect. 5), and behaviour (Sect. 6). Each section contains parts of the SDL language as examples. In the concluding Sect. 7, we discuss our results and suggest further work.

#### 2 Basics

In [9] meta-modelling is defined as: The construction of an object-oriented model of the abstract syntax of a language. However, in our article we use the term meta-model in a wider sense: A meta-model is a model that defines a language completely including the concrete syntax, abstract syntax and semantics.

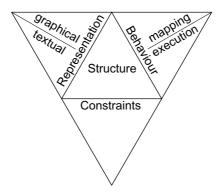

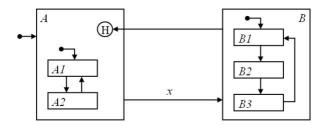

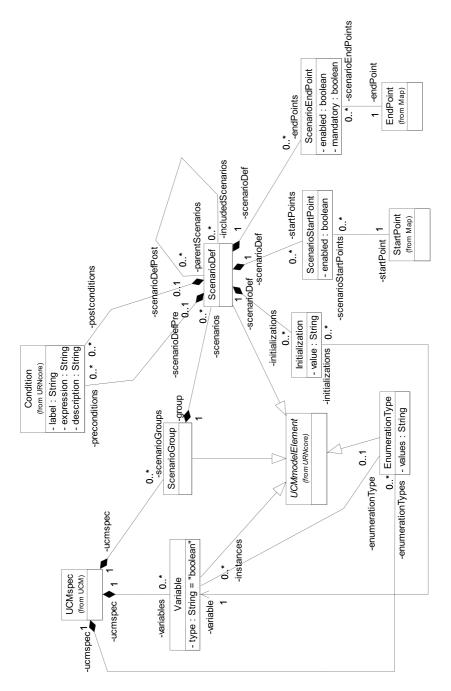

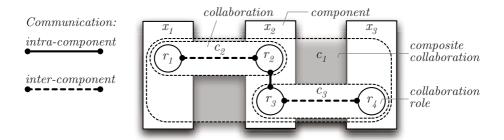

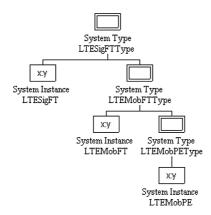

As a language description, meta-models can have several aspects that we have already identified in [10]. Figure 1 shows these aspects. Even though there is no complete agreement about what parts a language description consists of, these or similar parts can be identified in most contexts. The picture shows the following parts.

Structural information for the meta-model includes all the information about which concepts exist in the domain and how they are related. An example of this would be a MOF (Meta Object Facility) class diagram. In our understanding, this part does just include very simple structural properties and not more advanced concepts that rely on the use of constraints.

Fig. 1. Structure of a Meta-model

Constraints give additional information about the structure in that they identify the allowed structure according to additional logical constraints. This will include first-order logic constraints (e.g. written in Object Constraint Language (OCL)) as well as multiplicity constraints. In classical compiler theory these are collected under the name of static semantics and in a metamodel context they are called well-formedness rules.

Representation describes model serialization syntax and information about how the models are to be (re)presented to the user. The textual grammars (concrete textual syntax) are well understood in terms of compiler theory. When it comes to graphical grammar (concrete visual syntax), there is less agreement and there are some open research topics.

Behaviour describes how the model is used. This item includes execution of the model as well as mappings. By mapping we understand a relation between the model itself and another representation, e.g. in another language. A typical example would be a compiler from Java to JVM, or a mapping from a platform independent model to a platform specific model. An execution is the real run of the model, which is of course only possible if the model is executable. A typical example here would be a run of a Petri net.

In Fig. 1, the structure is the central aspect and all the other parts relate to the structure. The constraints have to be connected to the structural elements that they constrain. The representation parts describe the representation of elements in the structure, whereas the behaviour parts describe a behaviour for the elements defined in structure.

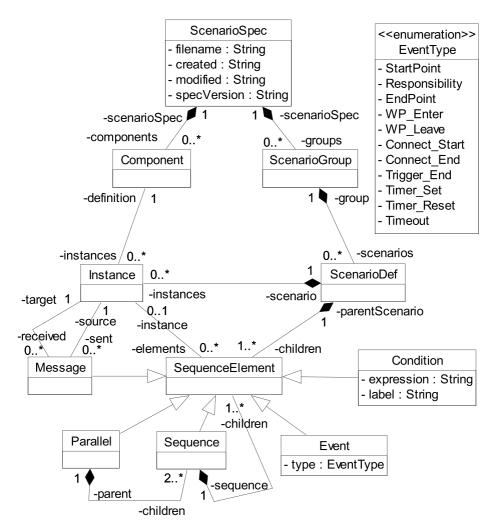

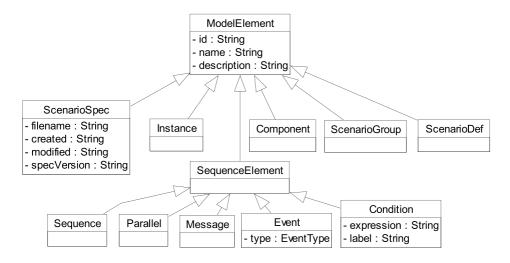

#### 3 Structure

The structure part of a language description defines an abstract data structure for models, programs, or specifications written in that language. Like in modeldriven development, object-oriented models in the form of class diagrams, are used in most meta-modelling architectures to model structures. These type models use classes as refinable classifications of entities by means of shared characteristics, modelled with attributes. Associations are used to classify the relations between entities. Associations are just a special kind of classifiers and actual links are a special kind of entities.

For a user-friendly description of the language, we use CMOF from MOF 2.0 [11]. CMOF (complete MOF) provides additional concepts to model abstractions compared to EMOF (essential MOF also part of MOF 2.0), which only defines a set of basic meta-modelling features. Examples for these additional CMOF features are property refinements, which allow to relate attributes or association ends in the context of classifier specialisation.

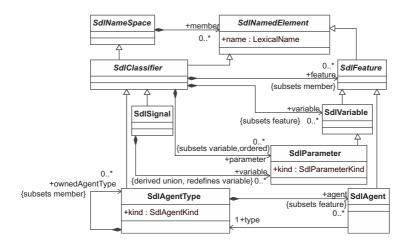

Fig. 2. Classifier concepts in SDL

In terms of languages, classes classify model elements based on the language concept that they instantiate. For example, all the agent types in all the existing SDL specifications are instances of the agent type concept. The first sample meta-model part in Fig. 2 describes the language concept agent type as a meta-model class. Attributes and associations are used to define the structural characteristics of agent types: an agent type can contain other agent types, it can contain type-based agents, it has parameters and variables. The example also shows how characteristics of more abstract language concepts can be reused. Agent types and signals for example, are just special SDL classifiers. SDL classifiers have features, like variables or parameters, as general characteristics. Variables are just one special form of features, and parameters just one special form of variables. Agent types inherit containment of variables and parameters and extend their set of features, containing variables and parameters already, with agents as just another type of feature. Signals inherit ownership of parameters. Signals also inherit ownership of variables and features, but only allow parameters as possible variables or features. The redefinition of the

property variable in signal as a derived union ensures that parameters are the only possible subset of variables.

Using all the CMOF features to express abstractions, enabled us to compose a meta-model for SDL from a predefined library of abstract language concepts. We re-used the UML infrastructure library accordingly to create the SDL meta-model. The UML infrastructure library was used to define the UML, so this approach makes sure that the two languages UML and SDL have a common base in their underlying language infrastructure.

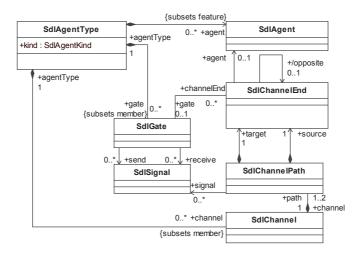

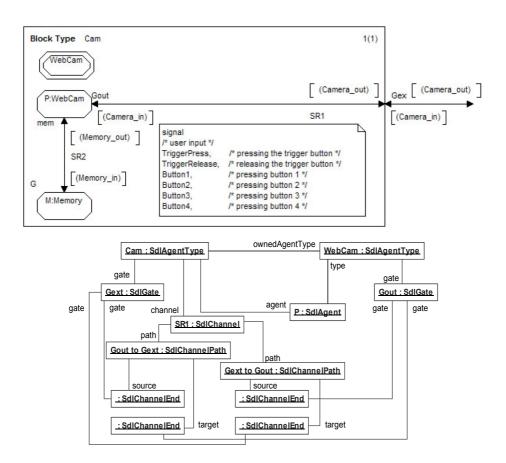

Fig. 3. Concepts for communication structures in SDL

Figure 3 shows another part of the SDL structure meta-model. This meta-model part covers the concepts of the sample specification in Fig. 4, which shows a block type definition (the entire example can be found in [15]). This block type definition is shown twice: in SDL syntax and as an object diagram, instantiating the SDL structure meta-model.

After having defined the structural meta-model in MOF 2.0, we had to find a proper tool supporting such descriptions. Although it is possible to find tools for MOF 2.0 (e.g. [13]), we decided to take a simpler tool which allows better integration with the other aspects as described in the next sections.

For the language tooling, we use Ecore (the meta-modelling language of EMF [1]). Ecore is a simple language allowing to express structures with just a few basic concepts. It is similar to EMOF. In Ecore the expressive power of the CMOF additional concepts has to be implemented manually, for example with OCL-expressions. Because of its simplicity, Ecore has the advantage of a clearer mapping to programming languages and more extensive tool support.

Compared with the SDL standard, the MOF-based structure definition yields almost the same object structure of a specification. The advantage is that it has much richer classification of the language concepts.

Fig. 4. Part of an example SDL specification and its model representation

#### 4 Constraints

Structure models are designed to define valid graphs of objects and links, by defining classes and associations. To complement these concepts of constructive modelling, we use boolean expressions to constrain the possible instances of a meta-model.

To define such static semantic rules for SDL, we use the Object Constraint Language (OCL) [12]. OCL is specifically designed as an expression language for object-oriented structures. It allows to define expressions based on types defined in a meta-model. These expressions, defined at meta-level, can then be evaluated on models. OCL is a statically typed language. Each formula is defined in the context of a meta-model type. Based on this context type an expression can use the features of the corresponding meta-element to navigate through models. OCL uses several predefined operators and functions to combine feature values into

a value for an OCL expression. Predefined functions and operators are derived from first order predicate logic.

We will illustrate the use of OCL with a sample constraint as given in the SDL standard. The text in Z.100 [8] is as follows:

The contained Agent-definitions of an Agent-definition with the Agent-kind PROCESS shall all have the Agent-kind PROCESS.

In the formal SDL semantics [7], this is formalised using first-order predicate logic to define expressions over abstract syntax as follows:

```

\forall d \in Agent-type-definition: (d.agentKind_1 = \texttt{process}) \Rightarrow (d' \in Agent-type-definition \cup Agent-definition: d'.parentAS1 = d \Rightarrow d'.agentKind_1 = \texttt{process})

```

In the meta-model, the same constraint is part of the context of SdlAgentType as follows:

In our approach the meta-model reflects the SDL structures as defined with grammars in the SDL standard. Therefore, we can use the same conditions from the SDL standard as a formal basis for corresponding OCL expressions. It is obvious that the two descriptions above match. The only difference is that in the meta-model-based OCL we navigated along object structures, instead of sets and nodes obtained from the abstract syntax tree in the grammar-based SDL standard. It should also be noted that the grammar-based SDL standard uses a complete view on all objects and uses logic to narrow onto the objects of interest. OCL, in contrast, starts with the object of interest and collects all other information from there.

Another sample constraint ensures compatibility of the two gates in bidirectional channels. It exemplifies the navigation through the more complex communication structures given in Fig. 3:

For defining all the constraints in the current SDL standard, it was necessary to define auxiliary functions. Fortunately, OCL allows arbitrary typed expressions and is thus also suitable as a query language, even though the name Object Constraint Language suggests that it can only be used for constraints (boolean

expressions). This allows to define derived and behavioural query features in meta-models based on OCL, as long as these features do not change the model. With derived properties and query operations, meta-modelling allows to define utility functions on the static SDL models based on simple OCL expressions. These utilities can be used in the realisation of other language aspects, such as the language behaviour. The following sample expression implements the association end attribute of SdlChannelEnd, which calculates the opposite channel end of the context channel end (self):

Finally, OCL can be used to express constraints that realise enhanced meta-modelling features. In Sect. 3 we argued that the simple meta-modelling language Ecore cannot be used to define the refinement of features. But those refinement expressions, provided by MOF 2, can be realised via OCL constraints. For example, for each redefined property there has to be an OCL expression that states that the redefined property always has the same values as the redefining property.

In summary, the OCL-based constraint definition is similar to the SDL standard regarding constraints and auxiliary functions. The main difference is that OCL is object-oriented.

# 5 Representation

In general, models are abstractions and do not have concrete appearance. But we need a concrete model representation to communicate them. Models in our minds need to be transformed into a concrete representation of the same model on a piece of paper or computer screen. Since model representations are the basis to exchange them with others, these representations need to be written in well defined model notations. All language users have to know the same notation in order to allow reasoning and exchange of models.

A notation is the definition of a model representation based on the structure meta-model. Hence, notations are defined at the meta-level. A notation defines a set of possible representations. Each representation represents a model of a corresponding meta-model. For describing a representation, we distinguish between three kinds of meta-models: the language structure meta-model; a model that describes the entities of our notation, the notation model; and a mapping model that connects these two models, mapping notation concepts to language concepts. All three models together provide all information necessary to provide model representations in a concrete notation. Of course, in simple situations it would be preferable with just one representation description. In Sect. 5.1 we give more reasons why it is necessary to consider an explicit mapping.

By separating notation model and structure meta-model, we allow to define multiple notations for the same language. In the following we describe textual and graphical representations for SDL models based on our SDL structural meta-model.

#### 5.1 Textual Representation

SDL is a language that has two syntax forms, a textual and a graphical. Although the textual syntax is moved out of the standard into a separate attachment, it is still an important format for tools and information exchange.

The textual syntax is not directly related to the meta-model of a language, which is more like an abstract syntax. Firstly, the textual representation contains information that is abstracted in the meta-model, such as indentation, comments or keywords. If this was the only difference, we could generate a unique concrete representation from a meta-model instance given some formatting instructions. However, SDL does also allow several representations for the same model construct. In fact, most programming languages allow this kind of flexibility, often referred to as *syntactic sugar*.

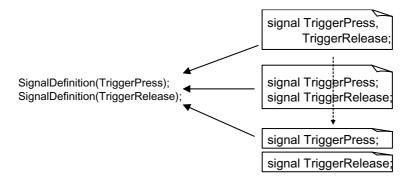

An example of this is given in Fig. 5 which shows the structure on the left-hand side and the representations on the right-hand side. All three representations have the same internal structure, with differences being in the graphical or the textual appearance or both. The solid arrows from the right-hand side to the left-hand side represent the semantic mapping from the representation alternatives to the same structure elements.

Please note that in the SDL standard, the mapping to the abstract syntax (i.e. the structure), is given by two mappings. The first mapping is called transformation and describes an in-place replacement within the concrete syntax. In Fig. 5, this is illustrated with a dashed line arrow. We might call this mapping a syntactic mapping. The second step in the SDL standard is an almost 1:1-mapping between the transformed concrete syntax and the abstract syntax.

Conceptually, the structure meta-model acts as the common core of all language elements. The concrete notation describes additions like keywords, comments, or

Fig. 5. Two concrete representations for an SDL construct

different syntactic forms. In order to capture this situation best, we use a direct mapping from the notation model to the structure meta-model. For textual representations, the notation model is given by a context-free grammar. The mapping model describes which concrete syntax elements refer to which meta-model elements.

As Fig. 5 illustrates, there might be several mappings from representation to model elements, as in the case of the signal definitions. We give the mapping for the signal definition below. We start with the concrete syntax description.

```

<signal definition>::=

signal <signal definition item>

{ <comma> <signal definition item> }* <end> .

<signal definition item> ::= <signal name> [<sort list>] .

<sort list> ::=

<left parenthesis> <sort> { <comma> <sort>}*

<right parenthesis> .

```

This definition is mapped to the meta-model using the following (uni-directional) transformation.

```

<signal definition>(items) ==>

{ SignalDefinition(name=i.name, sorts=i.sorts)

| with i in items }

```

A typical pattern in textual languages is the definition-use pattern. At some place an element is defined, and at some other place or even several other places the element is used. One may think of methods, variables, types or similar things. This situation is represented by an identifier in grammars, but by a direct link in a metamodel according to the type property in the type of association. This way identifiers only live in the textual representation and are almost useless for the meta-model.

Identifier resolution is formalised in the meta-model by a function *resolve* which does the resolution for an identifier given the complete SDL specification. This is done by defining an auxiliary function as detailed at the end of Sect. 4. The current SDL semantics has chosen the same approach by defining an auxiliary function *idToNodeAS1*.

Grammar and mapping can be used to automatically create an editor, which creates an SDL model according to the structure meta-model from user input based on the textual notation model. However, existing tools do only cover for a 1:1 mapping between concrete notation and structure meta-model. Therefore we did not pursue the concrete syntax to the end, and only created a parser from the description.

### 5.2 Graphical Representation

The graphical aspects of a language like SDL describe how the structural concepts are represented graphically. How is a block presented to the user? How should a system diagram look like? The graphical concepts are, like the structural concepts, related to each other. While the relations between the concepts in the structure describe how the language concepts are related to each other in a structural way, the

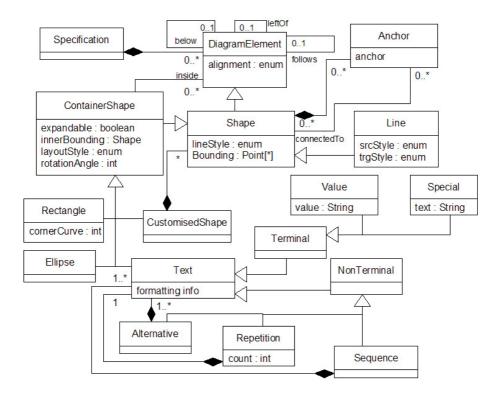

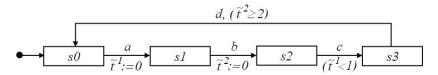

Fig. 6. Meta-Meta-Model for Graphical Representation

relations between the graphical concepts say something about how the concepts are related to each other graphically. The relations specify how the graphical concepts is related to each other to form valid diagrams in that language.

To be able to specify some kind of representation by structural meta-model (notation model), it is necessary to have a meta-meta-model for that. The meta-meta-model specifies the concepts and relations that are necessary to define the language graphics, in the same way that MOF or Ecore specify which concepts and which relations are allowed when defining a structure model (see Sect. 3). Figure 6 presents how the meta-meta-model for graphical notations looks according to our approach. This model defines the concepts that can be used to define a graphical notation.

The top-level element is the graphical Specification that consists of a number of Diagram Elements. These diagram elements are related to each other in one way or the other. A Shape is a diagram element, and there exist two main categories of Shapes-Container Shape and Line. A Container Shape is, as the name tells, a shape that can have other Diagram Elements inside itself. There are four different kinds of Container Shapes: Rectangle, Ellipse, Customised Shape and Text. One or more Anchors belonging to a Shape are used to specify where the Shape could be connected to another Shape. The Anchor is specified based on the property Bounding in Shape.

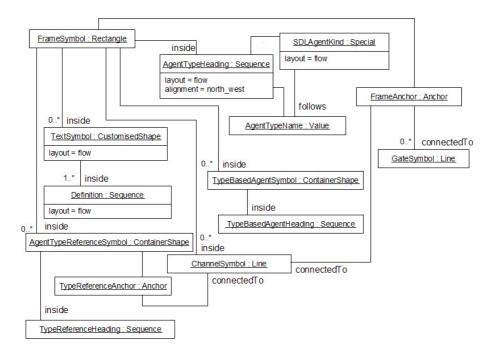

Fig. 7. SDL graphical meta-model for the concepts in Fig. 3

Most graphical languages do also include textual concepts, and how these textual concepts are handled must also be included in the meta-meta-model. Inspired by traditional grammar approaches for text handling, a *Text* element is either a *Terminal* or a *NonTerminal*. A terminal represents "words" in the language, and examples of a value from SDL are e.g. the name of an agent type, or an attribute. A *Special* textual element is another kind of terminal which models both keywords (e.g. **signal**, **use**) and special signs (e.g. ";", ":") which are all predefined. An example of a non-terminal is a text *Sequence*. A text sequence is in turn a composition of a number of other text elements (both terminals and non-terminals).

The meta-meta-model for graphical representation in Fig. 6 is at the same level as the MOF meta-meta-model in the OMG four level hierarchy. It makes it possible to specify the SDL graphical representation. To illustrate this, a small excerpt of the SDL graphical meta-model is shown in Fig. 7. The graphical concepts we see in this model, are some of the concepts that are necessary to model a block type diagram. They correspond to the concepts in the structure meta-model in Fig. 3.

The graphical model for SDL is mapped to the meta-model that specifies the structure. Since there should be a clear separation between these two language concepts, no direct references exist in the meta-models. This separation allows the exchangeability of different language notations. The mapping is a simple horizontal mapping from the graphical representation to the structure starting with the relation between the top elements.

FrameSymbol ==> SDLAgentType

The value of the SDLAgentKind in the heading of the diagram (from the graphics) is then mapped to the value of the AgentKind in the structure:

FrameSymbol.AgentTypeHeading.SDLAgentKind ==>

SDLAgentType.kind

This way, the mapping integrates the language aspects, and instances from the two meta-models are related in a correct way.

Unfortunately, there is no tool yet being able to handle such a graphics description. The best tool available in connection with Ecore is GMF (Graphical Modeling Framework)[6]. GMF is a framework that provides a platform for building graphical editors, and it acts as a bridging technology between the GEF platform [5] and the EMF modelling platform. GMF consists of two parts: the generative and the runtime part. The runtime part could be seen as a set of plug-ins extending the already existing EMF and GEF functionality. The generative part, on the other hand, is mainly covering the parts that make it possible for the user to define diagram editors using specially designed EMF meta-models and to generate code based on this information.

When defining the graphical representation in GMF, all the graphical concepts that are in the language and their appearance are specified in the graphical definition model (the notation model). The tooling definition model is an additional model that defines an editor toolbar and additional menu items, pop-up menus etc. These items can be used to modify instances of the graphical definition model. The graphical definition, the tooling definition and the structure definition (the .ecore file defined by EMF) are then bound together by using the mapping model. This mapping specification is then transformed into a generator model, which in turn is used to generate all the code necessary to run a diagram editor.

That far, the GMF approach maps nicely to our description. However, in practice GMF is only able to handle very simple specifications, in particular very simple relations in the mapping model. This means that we had to map the graphical model manually onto GMF, thereby losing much of its content. Of course, we gained also something as the tooling definition model is going beyond our description. The current graphical tool is adapted to fit the camera example as defined in [15].

Finally, we want again to compare our work with the existing standard. In the standard, both graphical and textual syntax are very loosely connected to the abstract syntax. Moreover, the notation to define the graphical syntax is not very formal. Our new definition solves all these deficiencies. However, still we do not have proper tool support.

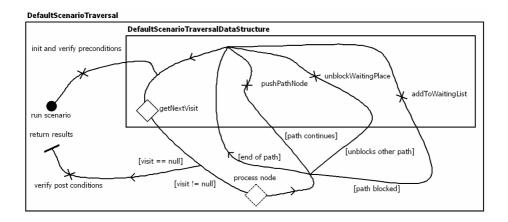

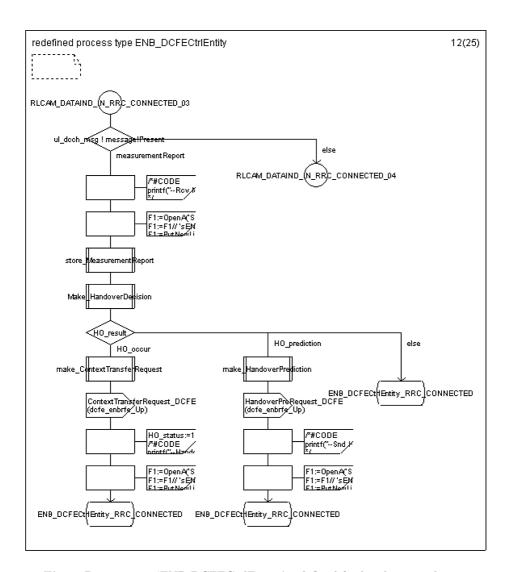

#### 6 Behaviour

In terms of behaviour (see again Fig. 1), for an SDL standard only the execution semantics is relevant. Mappings are interesting for SDL compiler tools, but not necessary to define the SDL behaviour.

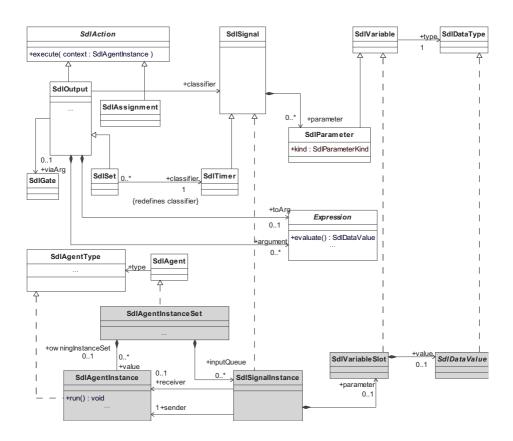

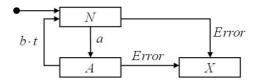

Fig. 8. Runtime elements for state automatons

To define the execution semantics we have to distinguish between two different kinds of structure elements, as detailed in [14]. The first kind describes abstract syntax elements; the structure model of SDL consists of such elements. The other kind of structure elements describes data that is needed at runtime. These runtime data include variable assignments, process instances, input buffers, etc. We therefore have to augment the regular structure description for SDL with descriptions for runtime data. The runtime elements are usually related to corresponding syntax elements, e.g. an agent instance at runtime level represents an agent type defined at syntax level. In a way, when creating instances of syntax elements, the related runtime representations are instantiated. This way the syntax elements function as factories producing related runtime elements. Figure 8 shows the syntax and runtime structure needed to describe the signal output action in SDL; syntax elements (white) are related to runtime elements (grey) by dashed arrows.

A similar distinction was also used for the SDL-2000 semantics [7]. Structural SDL elements were related to runtime elements defined as Abstract State Machines (ASM) [2]. Both were connected by an initialisation, i.e. an instantiation.

```

rule execute(o: Output, Self: SDLAgentInstance) =

let values = [evaluate(a,Self) | a in arguments(o)] in

SignalOutput(o, values, toArg(o))

currentStatement(Self) := continueStatement(o)

rule SignalOutput(s, vSeq, toArg) =

let invReference = (toArg memberof PId) and

(resolve(s) notin Signalset(Interface(toArg))

in

if not invReference then

choose g in ingates (Self) with Applicable (s, to Arg, g) do

extend SdlSignalInstance with si do

SdlSignal(si) := s

forall idx in Indices(vSeq) do

value(parameterValue(si)[idx]):= vSeq[idx]

receiver(si) := toArg; sender(si) := Self

Insert(si, now, g)

endchoose

endif

```

Fig. 9. Execution of output in ASM

Behavioural elements were translated to ASM runtime behaviour using a compilation function. This way, structural SDL elements relate to runtime elements with their corresponding abstract syntax counterpart. Behavioural SDL elements are just abstract syntax elements which do not need a separate runtime representation. The current SDL standard moves the behavioural elements into the runtime (ASM) domain using the compilation function. This is not necessary for the new approach, because all elements already live in the same domain. For our meta-modelbased approach, we replaced the compilation function by a direct use of the syntax elements. Instead of translating the SDL syntax tree elements into ASM elements, we use an ASM interpretation of the SDL elements, as it is done already now for the structural SDL elements. The ASM execution functions that shall run the model are attached to the corresponding syntax elements. Fig. 8 shows an example, where output is a syntax element with an execution function. The ASM execution function for the concrete SDL action signal output is given in Fig. 9. It might be interesting to note that the current ASM semantics takes a global view, i.e. all ASM agents can see everything (at least in principle). The new version is object-oriented in that it attaches the ASM code to the syntax or runtime objects. This is easily achieved starting from the current semantics, because it is now already formulated such that it refers to an executing object. The only thing we have to find out, is the context where the rule has to be placed.

In ASM, the context is shown by the parameters of the rules. As already stated in [14], the runtime elements have to have one context, whereas the syntax elements need two contexts: a runtime context and a syntax context. In the code in Fig. 9, Self denotes the runtime context, i.e. the actual agent instance. The syntax context

```

rule Run(Self:SdlAgentInstance) = // AgentProgram

if (agentMode1(Self) = initialisation) then

InitAgent

else if (agentMode1(Self) = execution) then

if ExecRightPresent(Self) then

ExecAgent

else

GetExecRight

endif

endif

```

Fig. 10. Run of an agent instance in ASM

(the *signal output* statement) is given by the first parameter in the rule. In terms of object-orientation this first parameter resembles the *this* parameter.

In a similar style, the behaviour for the runtime elements is given. One example here is a process instance as shown in Fig. 10. In the object-oriented model, this function is associated to a runtime object of type SDLAgentInstance, which is referred to in the ASM using the Self variable.

For the new dynamic description, we reused the existing ASM description many times. In order to achieve object-orientation, all semantic functions had to be attached to syntax elements or runtime elements. Moreover, the compilation function was not necessary any longer because the runtime actions were directly attached to the abstract syntax elements.

#### 7 Conclusions

In this article, we combined different technologies to create a description of SDL that covers the language aspects structure, constraints, representation, and behaviour. The resulting artifact can be used as a human readable standard, as well as a basis for the automated generation of SDL reference tools. A complete tools suite can be generated automatically: you can write an SDL specification in a generated SDL editor, check this specification, and execute it. We did this for the basic part of SDL. This restricted SDL was extensive enough to realise the camera example with the generated tools.

The resulting meta-model for SDL has some limitations and there are issues that couldn't be solved satisfactorily. The different language aspects, especially representation, require extensions and modifications of the language's structure model. This creates the additional burden of aligning different similar models with each other. Examples for this are representations that often provide different notations for the same language concepts; behaviour operations and constraints that have to be put into the structure model, even though the structure model is independent from these aspects. The presentation of the language description is another problem, because meta-models used for tooling are cluttered with technical information which is either not relevant for a standard or that a standard should abstract from.

Therefore, you need to describe more than necessary for a language standard to allow automatic tooling.

Compared to the SDL standard, our approach allows to utilize meta-model-based technologies that are more and more replacing grammar-based language development tools. The object-oriented meta-models allow for better reuse of abstract language concepts, and eventually lead to more coherent and compact language descriptions. The techniques used are mostly graphical and allow therefore easier human comprehension. Meta-modelling in combination with proper tooling, allows to display the language definition at different abstraction levels by omitting details thereby enhancing human understanding.

All this leads to a language standard that is a model. Of course, we can also have a printable document out of this model, but this is just another representation.

Future work will include further enhancements of language tools. Because those tools are generic tools parametrized through language descriptions, all languages immediately profit from further enhancements in this generic language tooling. Another important point is support for evolving languages. A language, as software, yields requirements that may change over time and therefore a language, its tools, and all the programs and specifications in a language may be subject to changes. Through the unification principle everything is a model, also meta-models profit from agile modelling techniques. General techniques like model transformations, or meta-model specific techniques like meta-model/model co-adaptation might be used to either evolve a language or to tailor a language to domain specific needs (profiling).

#### References

- 1. Budinsky, F., Steinberg, D., Merks, E., Ellersick, R., Grose, T.J.: Eclipse Modeling Framework (The Eclipse Series). Addison-Wesley Professional, Reading (2003)

- Börger, E., Stärk, R.: Abstract State Machines. In: A Method for High-Level Design and Analysis. Springer, Berlin (2003)

- 3. Eschbach, R., Glässer, U., Gotzhein, R., von Löwis, M., Prinz, A.: Formal definition of SDL-2000: Compiling and running SDL specifications as ASM models. In: Abstract State Machines 2001: New Developments and Applications, J.UCS Special issue, vol. 7(11) (2001)

- 4. Fischer, J., Holz, E., Prinz, A., Scheidgen, M.: Tool-based language development. Comput. Networks 49(5), 676–688 (2005)

- 5. Eclipse Graphical Editing Framework, See http://www.eclipse.org/gef

- 6. Eclipse Graphical Modeling Framework, See http://www.eclipse.org/gmf

- 7. ITU-T. SDL ITU-T Specification and Description Language, Formal Semantics. ITU-T Recommendation Z.100, Annex F (November 2000)

- 8. ITU-T. SDL ITU-T Specification and Description Language (SDL-2000). ITU-T Recommendation Z.100 (August 2002)

- Greenfield, J., Short, K., Cook, S., Kent, S.: Software Factories: Assembling Applications with Patterns, Frameworks, Models & Tools. John Wiley & Sons, Chichester (2004)

- 10. Nytun, J.P., Prinz, A., Tveit, M.S.: Automatic generation of modelling tools. In: Rensink, A., Warmer, J. (eds.) ECMDA-FA 2006. LNCS, vol. 4066, pp. 268–283. Springer, Heidelberg (2006)

- 11. OMG. Meta Object Facility (MOF) 2.0 Core Specification. Object Management Group, formal/2006-01-01 (January 2006)

- 12. OMG. OCL 2.0 Specification. Object Management Group, formal/2006-05-01 (May 2006)

- 13. Scheidgen, M.: A MOF 2.0 for Java. Humboldt-Universität zu Berlin, http://www.informatik.hu-berlin.de/sam/meta-tools/aM0F2.0forJava

- 14. Scheidgen, M., Fischer, J.: Human comprehensible and machine processable specifications of operational semantics. In: Akehurst, D.H., Vogel, R., Paige, R.F. (eds.) ECMDA-FA. LNCS, vol. 4530, pp. 157–171. Springer, Heidelberg (2007)

- 15. Tveit, M.S.: A Cinderella-based prototype of a digital camera— a contribution to the SDL'05 design contest. Telektronikk 2.2006 (2006), See also http://www.telenor.com/telektronikk/volumes/pdf/2.2006/

Page\_121-130.pdf

# Model Driven Development and Code Generation: An Automotive Case Study\*

Michele Banci<sup>1</sup>, Alessandro Fantechi<sup>1,2</sup>, Stefania Gnesi<sup>1</sup>, and Giovanni Lombardi<sup>1</sup>

<sup>1</sup> ISTI-CNR, Via G. Moruzzi 1, 56124 Pisa, Italy {michele.banci,stefania.gnesi,giovanni\_lombardi}@isti.cnr.it

<sup>2</sup> DSI - Università degli Studi di Firenze, Via S. Marta, 3, 50139 Firenze, Italy fantechi@dsi.unifi.it

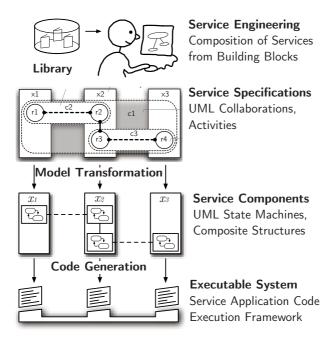

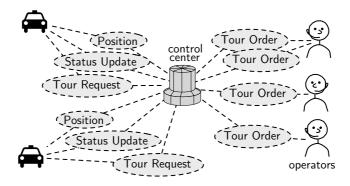

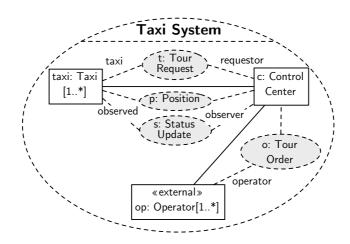

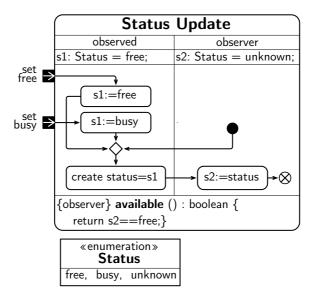

Abstract. Describing an application as a simple composition of services allows advanced features that exploit different platforms to be conceived and to be formalized at a high abstraction level. Several languages and formalisms have been proposed to this aim; UML diagrams are also used to this purpose. Starting from such an abstract description, still much work is needed to derive a working application, with a model-driven development process that needs to introduce and formalize many details. In this paper we report an experience in deriving an executable formal model from a high level specifications, originally given following a mainly architectural UML approach. The development process is illustrated on an automotive case study. A state of the art code generation tool is then applied to produce a prototype implementation of the analyzed system.

**Keywords:** Service-Oriented applications, formal modeling, automatic code generation, formal verification, formal validation.

#### 1 Introduction

Service-oriented computing is emerging as an interesting paradigm to describe, at various levels of abstraction, systems composed by dynamic assembly of classic computational entities, each of which provides a service to other entities, and which can be distributed over different platforms and communication networks.

Describing an application as a simple composition of services allows advanced features that exploit different platforms to be conceived and to be formalized at a high abstraction level. Several languages and formalisms have been proposed to this aim; the different languages adopted in the SENSORIA project [6] constitute an example of this variety.

In the very same project, UML diagrams have also been used to this purpose, and in particular have been used to give a first formalization to an automotive case study. This case study defines several services given to the future car user by application of mostly already available technology.

<sup>\*</sup> This work has been partially supported by the project SENSORIA, IST-2005-016004.

E. Gaudin, E. Najm, and R. Reed (Eds.): SDL 2007, LNCS 4745, pp. 19-34, 2007.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2007

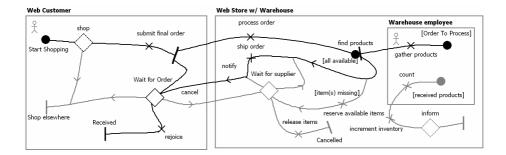

UML deployment diagrams, which give a static view of the architecture, have been used for a first formalization of the composition of services. A representation showing the evolution of the architecture was then required: for this purpose, UML sequence diagrams were used to represent the evolving connections within the service oriented architecture of the vehicle and its environment, and the interactions among services. Such an abstract description may serve as the starting point of a refinement process, that, by introducing implementation details, aims to produce a working prototype.

In this paper we report an experience aimed at producing an early prototype from such an abstract specification, through a first refinement step (from UML Sequence Diagrams to UML State Diagrams) and using an industrial strength, state of the art, modeling tool capable of automatic code generation. This requires a second refinement step, aimed at a more precise formalization of state machines. The tool used in this experience was SCADE. The method described in [2] to bridge the semantic gap between UML state diagrams and SCADE statecharts (SSM) has inspired the work we have done on the SENSORIA automotive case study. Formal verification has been used during the process to maintain consistency of the transformation between UML state diagrams and SSM.

The paper is organized as follows: In Sect. 2 we present the SENSORIA case study, by using both a natural language description and a first formal specification by UML sequence diagrams. In Sect. 3 we briefly introduce the SCADE tool and its formalisms, while in Sect. 4 we present the rules followed in order to translate the UML model into a SCADE model, and a description of the obtained SCADE model. Section 5 concludes the paper showing the prototype implementation, obtained by automatically generated code for the business logic wrapped in a communication interface to provide the implemented services.

# 2 SENSORIA Case Study

Today's embedded computers in cars can access communication networks like the Internet and thereby provide a variety of new services for cars and drivers. A set of possible scenarios of the automotive domain have been examined within the scope of the SENSORIA project, among which we select a car repair scenario low oil level for illustrating the different techniques presented in this article.

Some of the functionality described in the scenario are already integrated in modern vehicles; other functionality might be available to drivers in the near future.

We have chosen this scenario because of its complexity, in which all aspects of service interaction can be studied.

The actors and their interaction with the system in the scenario are the following:

- Sensor systems: cause low oil level alert

- **Discovery engine:** discovers services needed (towing, repair)

- Driver: communicates with towing and repair service

- Tow truck: receives GPS co-ordinates of stranded vehicle

- Repair shop: receives diagnostic data from stranded vehicle

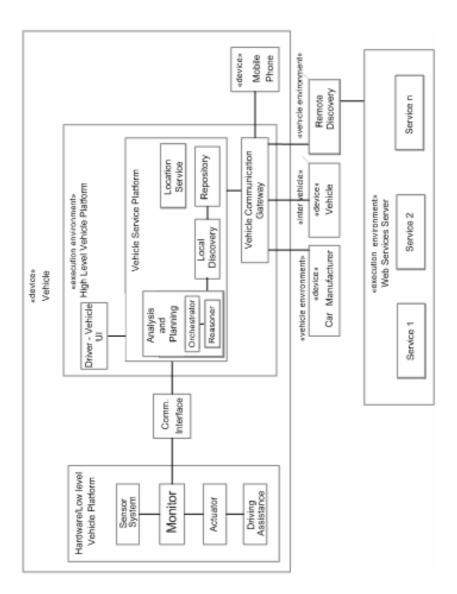

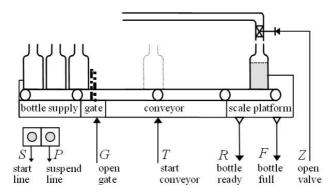

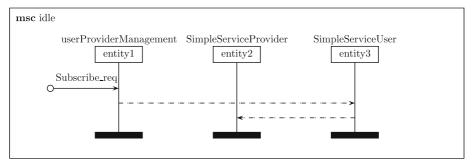

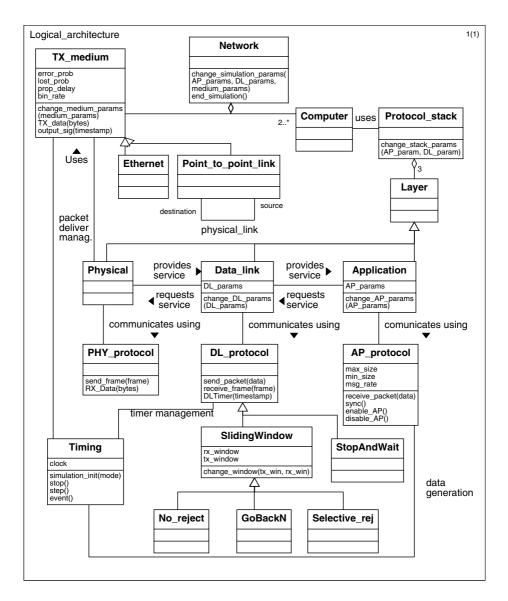

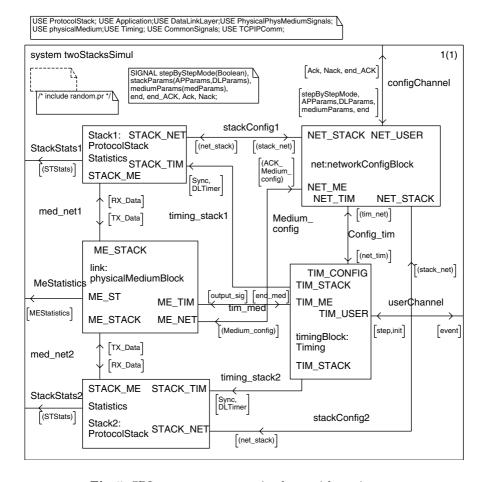

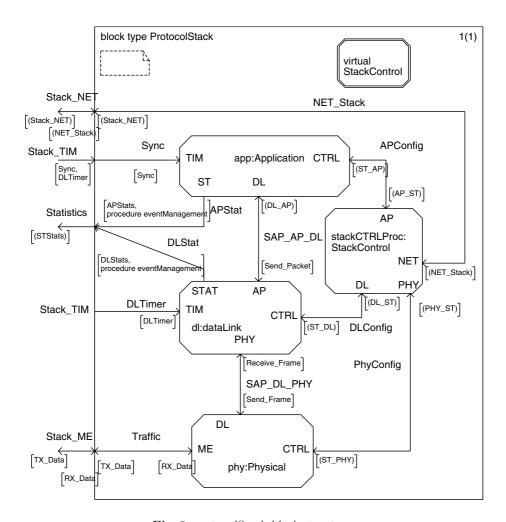

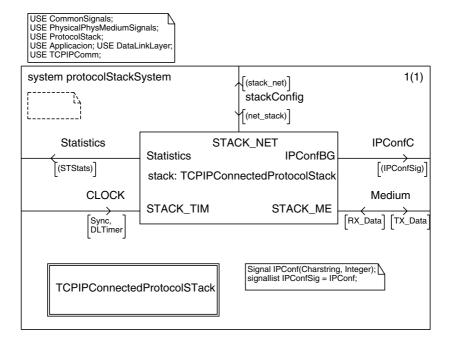

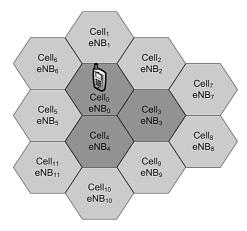

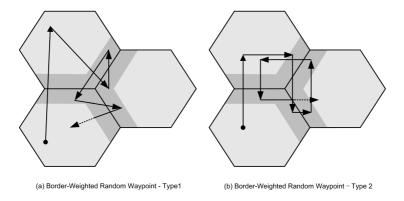

Fig. 1. Modules of simplified automotive service architecture

The sensor systems cause an in-vehicle diagnostic system to check why the oil level has reached a minimum. The result of the diagnostic system is passed on to the discovery engine, which then locates the appropriate services needed (adequate repair shop, tow truck) based on the diagnostics, the driver's preferences and the location of the vehicle.

The main components of the overall car system architecture (as seen in Fig. 1) that are involved in this scenario are:

- 1. **Service Planning**: is a specific software vehicle component, it manages some events (e.g. anomalous sensor data) and reacts to dedicated enabling services (e.g. In-car diagnostic service).

- 2. **Communication System**: enables communication between internal and external services of the vehicle.

- 3. **In-car diagnostic service**: is an In-Vehicle integrated service, analyses events reported by the Service Planning, and produces a problem description.

- 4. External diagnostic service: is provided by the vehicle producer. Data sensors and the vehicle state are sent to a dedicated server where they are analyzed and compared to a diagnostic errors database; this server's answers provide a correct diagnosis.

- 5. On road repair service: is an external service that performs an automatic repair service reservation.

#### 2.1 Low Oil Level Scenario by UML Specification

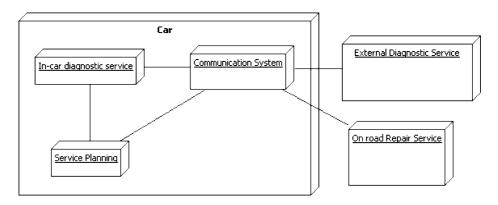

The structure of a service oriented architecture can be visualized by UML deployment and composite structure diagrams. A deployment diagram is used to represent the (usually nested) nodes of the architecture such as hardware devices or software execution environments. Figure 3 shows a UML deployment diagram of the car and its environment as a first approximation of an architecture model related to architecture of the low oil level scenario.

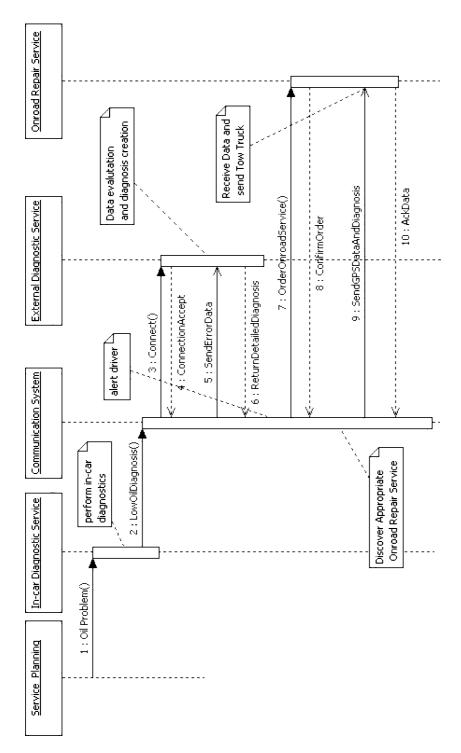

In addition to UML deployment diagrams, which give a static view of the architecture, a representation showing the evolution of an architecture is required. UML sequence diagrams have been used to represent the evolving connections within the service oriented architecture of the vehicle and its environment.

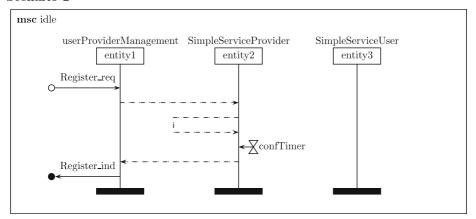

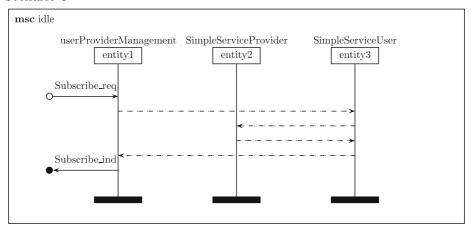

Several scenarios of evolution have been described using sequence diagrams. In the following we show some of them; the so called "success" scenario, that refers to the normal way of operation, is presented in Fig. 4, while Fig. 5 and Fig. 6 represent alternative scenarios.

The two alternative scenarios presented here are related to two error situations: other error situations concerning special cases have been considered and have been singularly modeled by sequence diagrams.

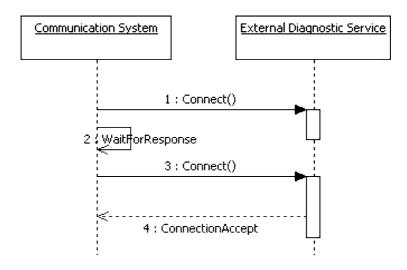

1. Time Out error: The Communication System tries to connect to the External Diagnostic Service, which is unable to answer (connection error); after a predefined time interval the communication system retries to connect; this procedure is repeated until a connection is established.

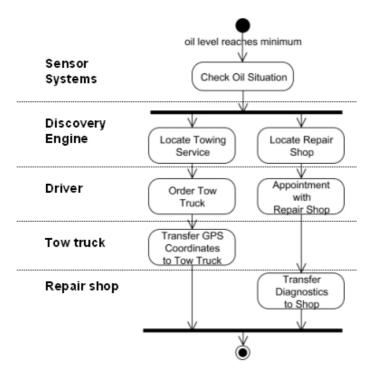

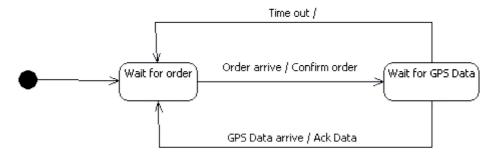

Fig. 2. System Flowchart

Fig. 3. Low Oil Level Deployment Diagram

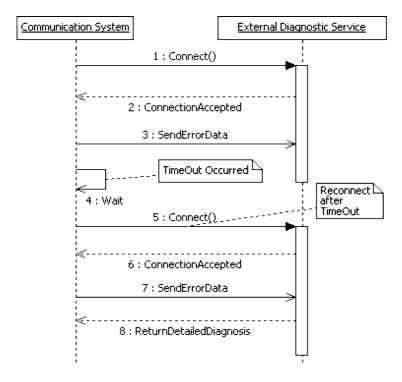

2. Send & Receive data error: After establishing a connection with the External Diagnostic Service, the vehicle GPS coordinates and diagnostics data are automatically sent to the External Diagnostic Service at regular intervals by the communication system; if the communication system obtains no answers by the External Diagnostic Service, then the vehicles data will be automatically sent to the External Diagnostic Service at regular intervals by the communication system until the service provides an answer.

Fig. 4. Low Oil Level Sequence Diagram

Fig. 5. - Time Out error - Low Oil Sequence Diagram

${\bf Fig.\,6.}$  Send & Receive error - Low Oil Sequence Diagram

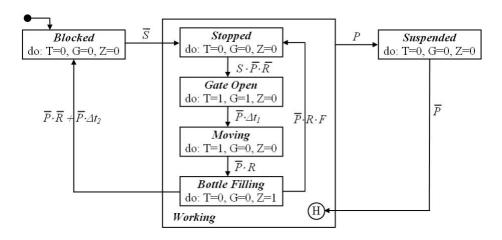

Fig. 7. Communication System

Fig. 8. External Diagnostic Service

Fig. 9. On Road Repair Service

#### 2.2 Sequence Diagram

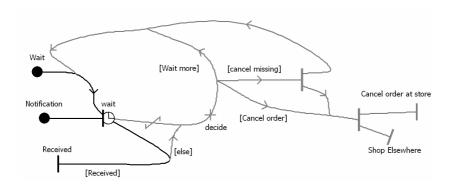

The synthesis of State Diagrams from Sequence Diagrams has been extensively studied in the literature: [9] presents a survey of these works, while the first application to UML Sequence and State Diagrams can be found in [7].

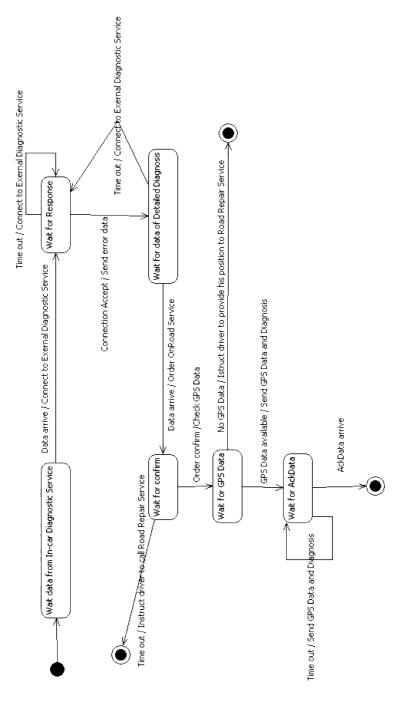

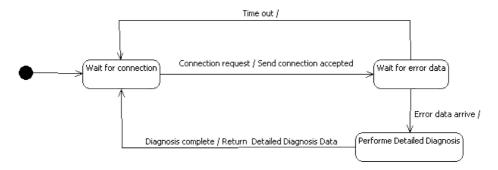

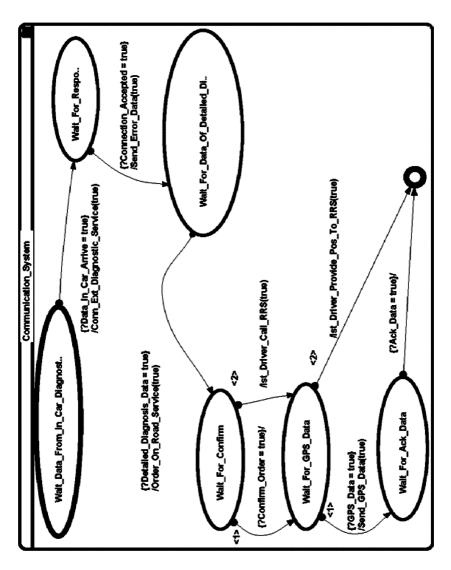

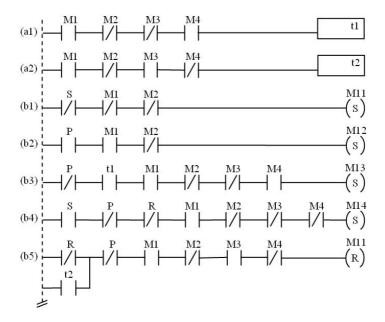

The UML state diagrams related to the main classes involved in the low oil level scenario are given in Fig. 7, Fig. 8 and Fig. 9.

The State Diagram in Fig. 7 represents the behavior of the in-car communication system that have been implemented merging the above mentioned sequence diagrams. The State Diagrams in Fig. 8 and Fig. 9 represent two other external actors that provide the services.

A formal verification over the obtained state diagrams can be done in order to check that the synthesis process has not violated some desired safety or liveness properties, by means of model checking. The model checker UMC for UML state diagrams and the UCTL state-action based temporal logic has been used for this purpose (see [1,8] for a description of UCTL and UMC).

A typical property of interest in this case is for example: "If a low oil level alarm is raised, then if no time-outs of any sort occur, a towing truck is eventually called" that can be expressed using UCTL as:

AG[OilProblem](< TimeOut > true | AF < OrderOnRepairservice > true)

### 3 The SCADE Tool-Suite

The SCADE (Safety Critical Application Development Environment) tool-suite by Esterel Technologies is a set of tools able to support a whole model-based development method. SCADE is mostly used in automotive and avionics applications, and relies on diagrams and state machines, represents a graphical approach to formal method. Its graphical modeling formalism benefits from deterministic formal semantics, allowing the derivation of a clean mathematical model from a SCADE design to the synchronous paradigm of the Lustre [4] language. The same deterministic model can be used for correct-by-construction automatic code generation and formal verification [5].

SCADE provides a verification technique based on formal verification tools over the model as well.

#### 4 From UML SD to SCADE SSM

The process we have followed in transforming the UML state diagrams to SCADE Safe State Machines is inspired to that described in [2].

In particular, each UML State Diagram is directly mapped to a SCADE SSM, due to the similarity of their internal structure. This step has been carried out manually.

However SCADE is based on the synchronous data-flow paradigm. Inputs and outputs of a SCADE block are typed data-flows. The type of a data-flow can be simple (bool, int, real) or structured (a structure or tuple made of a set of typed fields).

A SSM is a particular kind of block, so the messages and stored variables that are used in UML to synchronize two State Diagrams have to be transformed into data flow between blocks.

In the special case when the first field of a structured input data-flow is of type bool (or when the input data-flow's type itself is bool), this boolean value can be used as a "signal presence status" in triggers of transitions in SCADE Safe State Machines. Symmetrically, when the first field of a structured output data-flow is of type bool (or when the output data-flow's type itself is bool), this boolean value represents the "signal presence status" of the output signal, set to true if and only if the signal is emitted during the execution of a SCADE node. Input or output flows associated with such a Boolean presence status can be used to represent sporadic or transient signals which are considered only for some specific executions of the SCADE node.

#### 4.1 The SCADE Model

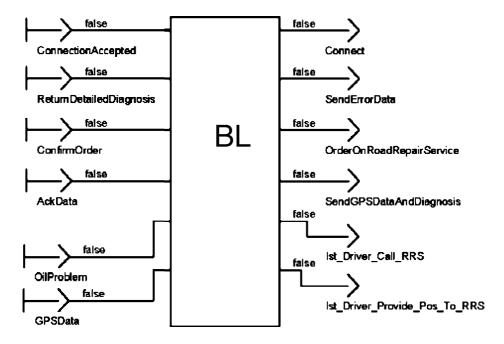

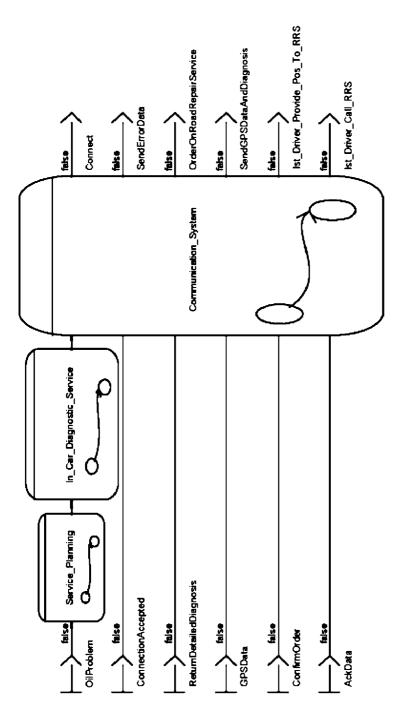

The SCADE formal model of the Low-Oil-System uses SSMs (Safe State Machines) encapsulated into block diagrams as illustrated in Fig. 10, Fig. 11 and Fig. 12. The global system named Low-oil scenario has been sliced in three different models: the in-car subsystem and two out-car subsystems representing the diagnostic system and the car repair shop.

The modeling methodology used is the same for each subsystem, so we will illustrate only the in-car subsystem model. The main object of this subsystem is a generic high level data-flow block (Fig. 10). This main block includes three interconnected SSMs (Fig. 11). To this block input data flows from the in car sensors system and from a gateway connected to external services arrive. From this in-car system several signals are sent to the out-car services.

Fig. 10. Main in-car block

Although SCADE provides several kinds of data flow blocks we have modeled our system using state machines only, for a direct correspondence to the UML State Diagrams.

Figure 12 shows the main state machine, namely the Communication System, which is actually similar to the corresponding UML one of Fig. 7.

### 4.2 Formal Verification of Safety Requirements

In order to validate the performed transformation on the models developed using the SCADE tool, several functional test scenario have been verified using the SCADE simulator.

Moreover, the same properties that have been verified over the UML state diagram model have also been verified over the SCADE state machines by means of the native model checker Design Verifier tool, in order to check that the transformation to SCADE has not introduced violations to the desired properties.

Fig. 11. SSMs describing the in-car system behaviour

Fig. 12. The Communication System SSM

The property defined above for the UML model can be expressed on the variables of the SCADE model as:

When the low oil sensor has become true and there are no time out errors then the repair shop has to acknowledge the request sent to it (see Fig. 4).

The SCADE expression of the property has the form:

ServicePlanning(OilProblem)  $\land \neg CommunicationSystem("TimeOutOccured")$  $\Rightarrow OrderOnRoadRepairService(AckData)$

in which temporal aspects are however not represented. These are actually taken into account in the graphical expression, displayed in Fig. 13, by memory elements that record the occurrences of the events.

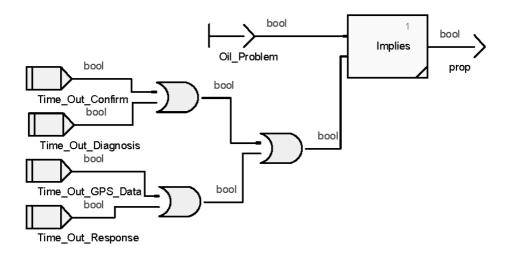

Fig. 13. The safety properties in SCADE

The verification of this property initially highlighted a problem about the implementation of the time out manager: after fixing this misbehavior the property has shown to be valid.

# 5 From SCADE Model to Code Prototype

After the model verification, the system constituted by three state models has also been implemented using the capabilities of the automatic code generator.

To perform the simulation, some user interfaces have been implemented and mapped to the model using a gateway provided by the SCADE tool. After the environment supported simulation these user interfaces have been reused to stimulate the automatically generated code.

At the end of the whole development process we have obtained three independent systems, communicating by TCP/IP sockets, each of them exposing one or more services. The simulated stimuli from the in-car side have been sent by the above cited user interfaces.

The final structure is similar to that illustrated in the deployment diagram of Fig. 3.

The complete prototype consists of some generic parts (the user interfaces and the TCP/IP communication modules) and some specific parts (what is often called "business logic"), that have been automatically generated in C language directly from the models. At the end of the development phase we have obtained:

- 1. C code automatically generated by the SCADE tool and representing the model behavior.

- 2. Generic wrap code to build a dll containing the business logic C code above .

- A generic TCP/IP module, to communicate with the environment (the other two models: on road repair shop, external diagnostic services) that provide services and vice versa.

- 4. An On Board Console (see Fig. 14) that is the user interface to simulate the in-car sensor layer.

Fig. 14. On Board Console

The different parts have then been integrated in order to build an application able to simulate the scenarios from which we have started the development process, with all the concerned interactions.

### 6 Conclusions

We have reported an experience in deriving an executable prototype from a high level specification of a service oriented application related to an automotive case study. The experience has been made inside a research effort aiming at defining a complete model-driven development process from high level specifications to executable code, based on industrial-strength tools.

In particular the purpose of the experience was to evaluate the adoption of a tool like SCADE, which allows for code generation, formal verification and test case generation, to refine the partly formalized UML state diagrams of the original specifications, with state machines having a formal semantics.

The followed development process, starting from a UML sequence diagram description of typical usage scenarios of the automotive case study, has included first the synthesis of UML state diagrams from the sequence diagrams and then a refinement step mainly based on the translation of the state diagram model into an executable SCADE model. Despite some semantic differences between the two formalisms, this translation has proved straightforward. Formal verification by model checking has helped to check the semantic consistency of the transformation.

The obtained SCADE model has allowed to exploit automatic code generation. The generated code has then been embedded in a communication framework that in the end has made it possible to produce an executable prototype of the initial specification. The proposed development process, despite the usage of different formalisms, has resulted to be effective in producing in a short time a working prototype from the original concept, thanks to the supporting tools (model checkers, simulators and code generators) used at the various steps.

### References

- 1. Model Checker for UML Statechart Diagrams, fmt.isti.cnr.it/umc/

- 2. Le Guennec, A., Dion, B.: Bridging UML and Safety-Critical Software Development Environments, ERTS, Toulouse, France (January 2006)

- 3. Brooks, C., Lee, E.A., Liu, X., Neuendorffer, S., Zhao, Y., Zheng, H.: Heterogeneous Concurrent Modeling and Design in Java. Memorandum UCB/ERL M04/27, EECS, University of California, Berkeley, CA USA 94720 (July 2004)

- 4. Halbwachs, N., Caspi, P., Raymond, P., Pilaud, D.: The synchronous dataflow programming language lustre. Proceedings of the IEEE 79(9), 1305–1320 (1991)

- 5. Raymond, P.: Compilation efficace d'un langage d'eclaratif synchrone: le generateur de code Lustre-v3. PhD thesis, Institut National Polytechnique de Grenoble (1991)

- Wirsing, M., Clark, A., Gilmore, S., Hölzl, M.M., Knapp, A., Koch, N., Schroeder, A.: Semantic-Based Development of Service-Oriented Systems. In: Najm, E., Pradat-Peyre, J.F., Donzeau-Gouge, V.V. (eds.) FORTE 2006. LNCS, vol. 4229, Springer, Heidelberg (2006)

- Whittle, J., Schumann, J.: Generating statechart designs from scenarios. In: ICSE 2000. Proceedings of the 22nd International Conference on on Software Engineering, Limerick Ireland, June 4-11, 2000, pp. 314–323. ACM, New York (2000)

- 8. ter Beek, M.H., Fantechi, A., Gnesi, S., Mazzanti, F.: An action/state-based model-checking approach for the analysis of an asynchronous protocol for Service-Oriented Applications. In: Brim, L., Haverkort, B., Leucker, M., van de Pol, J. (eds.) FMICS 2006 and PDMC 2006. LNCS, vol. 4346, Springer, Heidelberg (2007)

- 9. Liang, H., Dingel, J., Diskin, Z.: A comparative survey of scenario-based to state-based model synthesis approaches. In: SCESM '06. Proceedings of the 2006 international workshop on Scenarios and state machines: models, algorithms, and tools, Shanghai, China, pp. 5–12. ACM, New York (2006)

# Experiences in Deploying Model-Driven Engineering

Thomas Weigert, Frank Weil, Kevin Marth, Paul Baker, Clive Jervis, Paul Dietz, Yexuan Gui, Aswin van den Berg, Kim Fleer, David Nelson, Michael Wells, and Brian Mastenbrook

Motorola Schaumburg, Illinois, USA thomas.weigert@motorola.com

Abstract. In this paper, we describe how Motorola has deployed model-driven engineering in product development, in particular for the development of highly reliable telecommunications systems, and outline the benefits obtained. Model-driven engineering has dramatically increased both the quality and the reliability of software developed in our organization, as well as the productivity of our software engineers. Our experience demonstrates that model-driven engineering significantly improves the development process for telecommunications systems. We discuss the elements we found most important for deployment of model-driven engineering in a large product development organization: An appropriate modeling language, a powerful domain-specific code generator, and a deployment support team.

### 1 Introduction

Motorola has more than 15 years of history deploying model-driven engineering techniques to develop highly reliable network elements for large-scale telecommunication systems. Model-driven engineering has dramatically increased the quality and reliability of the developed software as well as the productivity of the software engineers [1].

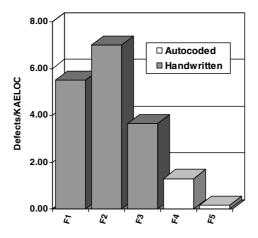

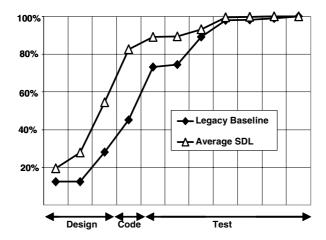

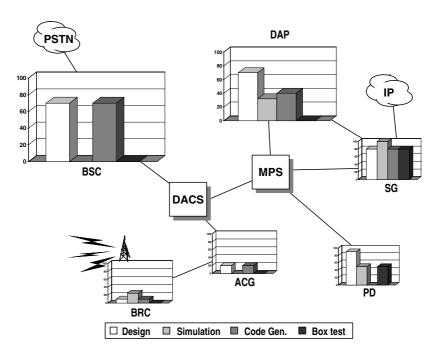

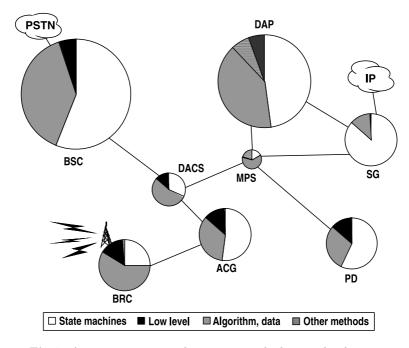

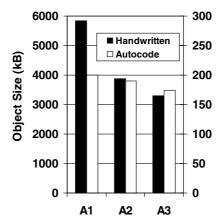

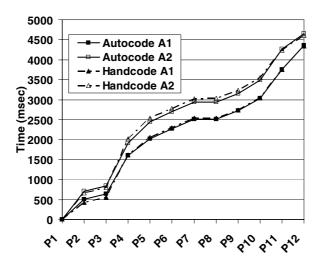

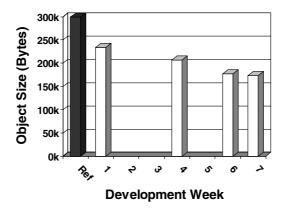

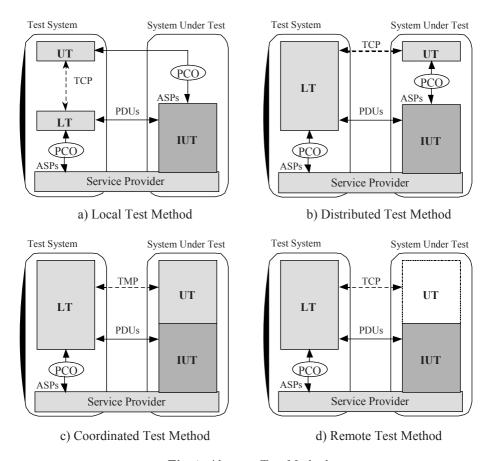

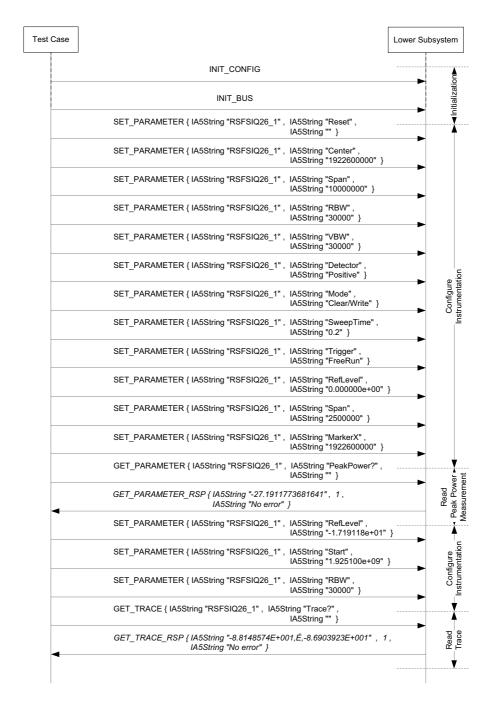

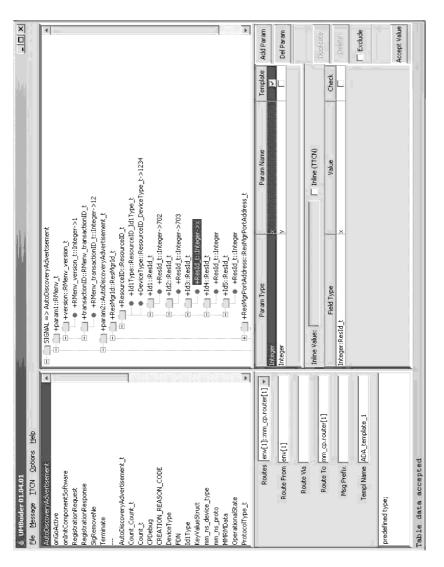

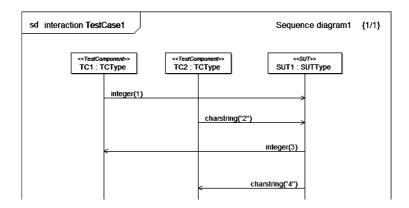

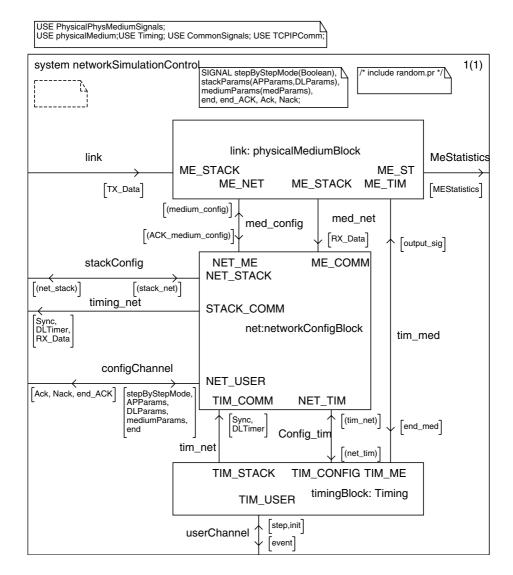

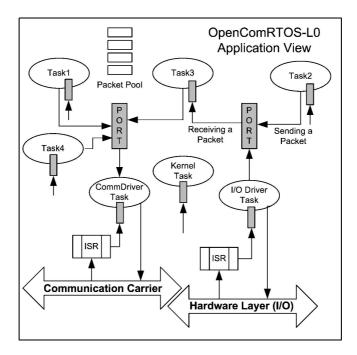

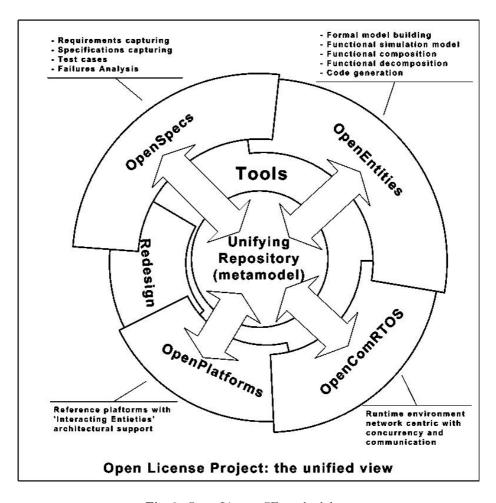

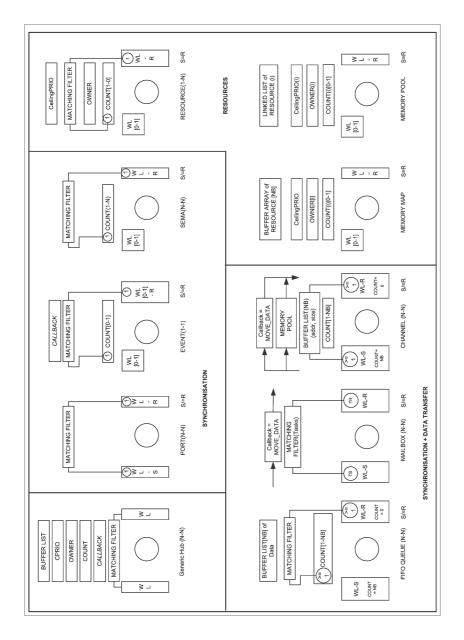

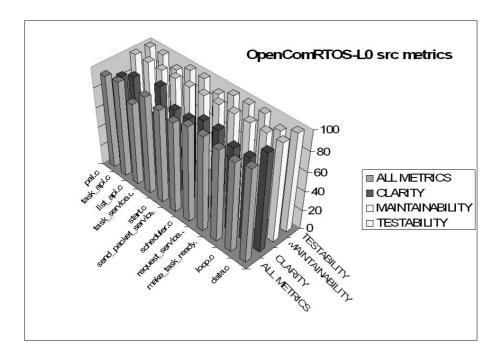

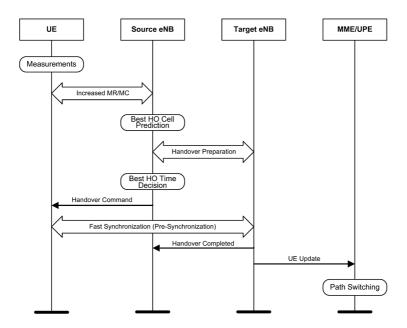

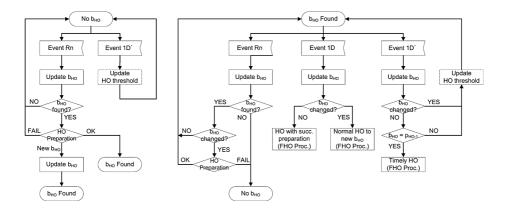

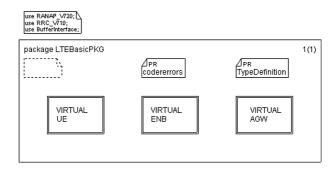

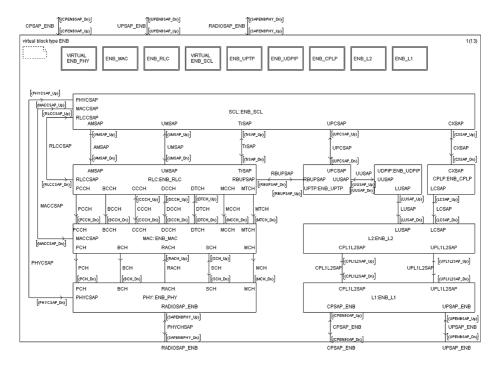

This paper describes the model-driven engineering approach Motorola has been deploying. Model-driven engineering relies on capturing an application design in domain-specific languages; in Motorola, specifications are expressed using UML profiles [2,3] such as the SDL Profile [4], using ASN.1 [5], or using customized protocol-specification languages [6]. In the telecommunications domain, the basic domain abstractions are asynchronous, communicating processes based on finite-state machines and protocol data units. The specifications are subject to validation by operationally interpreting the specification and through executing formally defined test cases (written at the level of the design model in a test-specific notation, typically, but not exclusively, TTCN [7]) against this specification. Domain-specific programming knowledge is captured in code generators that transform the high-level designs into optimized product software targeted to the chosen platform.